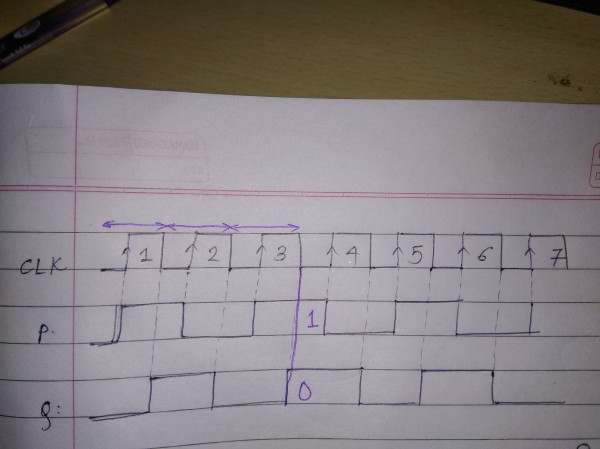

-> As there is Master Slave configuration, 1st flipflop will respond to the positive edges and the 2nd flipflop to the negative edges.

-> As the given Flipflops are synchronous,(clock is simultaneously given to both FFs) $Q$ responds according to immediate values of $P$.

-> Thus, after 3 cycles, as shown in the diagram, $P = 1$ and $Q=0$