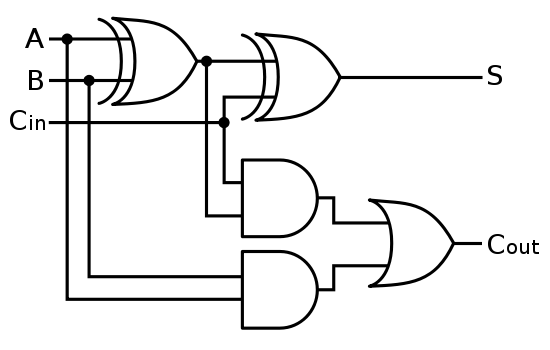

$S1$ should wait for $C1$ to be ready. Delay for generating $C$ is $1$ EXOR $+ 1$ AND $+ 1$ OR $= 2.4 + 1.2 + 1.2 = 4.8\;\mu s$

Delay for sum is XOR + XOR $= 2.4 + 2.4 = 4.8\;\mu s$

But for the second adder, there the first EXOR can be done even before waiting for the previous output. So, we can get the sum in Another $2.4\;\mu s$ and carry in another $2.4\;\mu s$. In this way, $4\text{-bit}$ sum can be obtained after

$4.8\;\mu s + 3 \ast 2.4 \;\mu s = 12\; \mu s.$

But the question says we use ripple-carry adder. So, each adder must wait for the full output from the previous adder. This would make the total delay $= 4 \ast 4.8 = 19.2\;\mu s$ and this is the key given by GATE, so obviously they meant this.