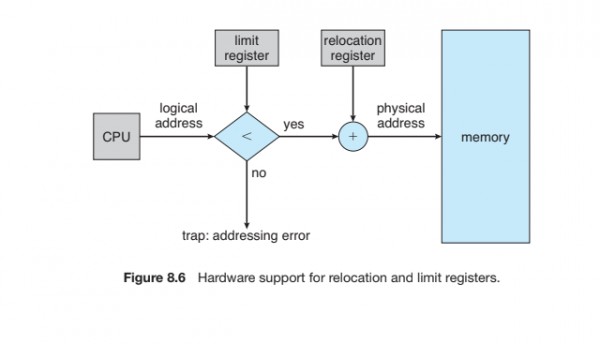

Limit : contains the range of logical addresses (i.e. size of the range)

Base and relocation reg: holds smallest legal physical address

There is another figure in Galvin which checks the logical address with the limit first and if the address is within the range (i.e. less than limit) then MMU maps the logical address dynamically by adding the value in the relocation register. So if the address generated by CPU is A then

in short : if A <Limit then Map(A+reloc).

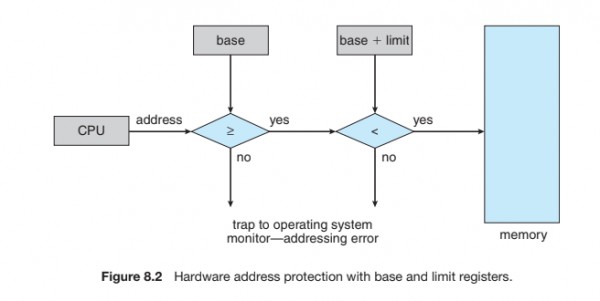

In Ayush's figure, the logical address is first checked with the base. If address is more than equal to base then again it is checked with (base+limit).

Base <= A <Limit+Base

If the condition is satisfied then A has to be mapped to some physical address ( this is done by MMU).

So in both cases address translation is needed in the last step.