i try to solve this question it is bit typical ..

note- it is just only my intitution ..

Below in table you can see there is three input a,b and c and two output Sum and carry which is represented as s and c2.

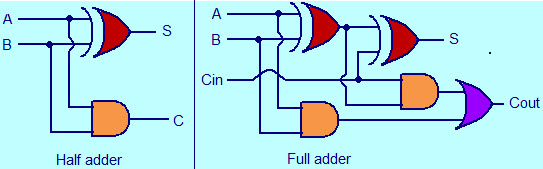

now in c2 which is carry there are four one which means four carry are genrated according to question carry takes 5ns propagation delay so 5*4= 20 ns now in full adder circuit when you make k map for sum and carry and you realiize them you can see there are exatly two and gates and two or gates. so each and gate takes 2ns so total 4ns now 20 ns * 4 = 80ns

multiplication of 8 bit number using array miltiplier means 1 bit take 1ns so total 8ns so therefor 80-8=72ns

| a |

b |

c1 |

s |

C2 |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

1 |

| 1 |

0 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

1 |

| 1 |

1 |

0 |

0 |

1 |

| 1 |

1 |

1 |

1 |

1 |