For future readers : Don't read it..instead check the links attached here https://gateoverflow.in/250088/cycle-stealing-dma-doubt?show=285767#c285767

A bit of background:

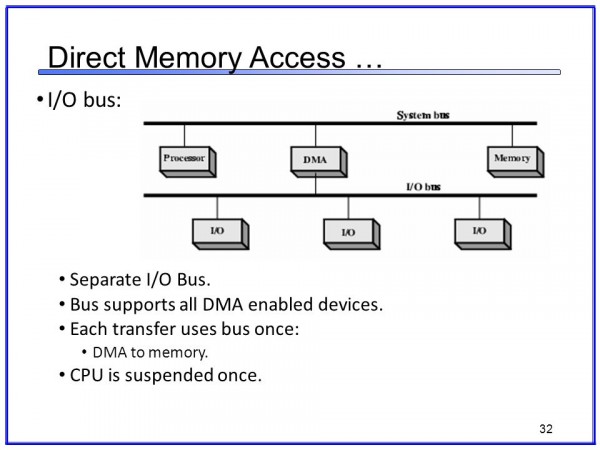

The hard disk has to send some data to MM. It should take the help of processor to do so. When CPU gets an interrupt signal from any I/O device, then it asks the DMA controller to handle the interrupts and transfer data b/w the I/O device and the memory. For that CPU has to surrender it's control over memory bus for some time.

Then you might think what will CPU do now without the bus..will it sit idle...if yes then what is the use handing bus control to DMA..if no then what keeps CPU engaged?

CPU can carry out other instructions which do not require memory like ADD/SUB two register variables. So at this time parallely the DMA works on the transferring b/w I/O and main memory while the CPU handles instructions which do not require MM.

But there might arrive a situation where CPU may require the MM for eg to execute LOAD/STORE instructions. But since DMA has the control over the memory bus CPU has to wait till it gets it back. So at this time the CPU activity gets slowed down by some amount.

Note that while data is being transferred from I/O to DMA buffer we don't need memory bus and only I/O bus is required. Once the buffer is full meaning that DMA is ready to transfer data to MM, it asks the CPU to give the control over memory bus.

So steps are :

1) I/O generates interrupt.

2) CPU asks DMA to handle it.

3) I/O transfers data to DMA using I/O bus.

4) Once DMA buffer is full (data ready) it asks CPU to relinquish the memory bus.

5) CPU gives the memory bus to DMA.

6) After DMA finishes transferring it gives back the control to CPU.

There are some modes in which CPU and DMA work. One of them is cycle stealing mode.

Initially CPU is having control over MM through MM bus. Now data is ready in DMA buffer. It has to take the bus from CPU. Meanwhile CPU cannot carry out it's tasks which involved MM. So CPU is slowed down a bit as the DMA "stole" it's cycles. "Stealing a cycle" means taking control over the bus. DMA transfers 1B per cycle and then releases the bus.

Other mode is Burst mode where DMA possesses the bus as long as the whole data in buffer is not transferred to MM. Another is transparent mode(not reqd for Gate i guess).

This topic has troubled me a lot and all these are my conclusions after going through various resources. If you find anything wrong then point it out.