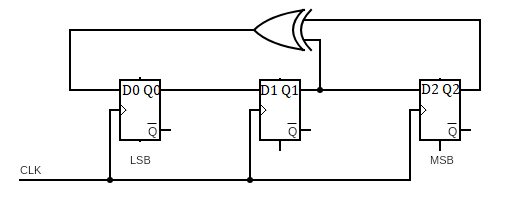

The diagram of FF is:

According to figure, we can write next state as:

$Q_{0N}=Q_1 \oplus Q_2, Q_{1N}=Q_0,Q_{2N}=Q_1$

Transition table can be given as:

| Q2 |

Q1 |

Q0 |

Q2N |

Q1N |

Q0N |

| 0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

1 |

0 |

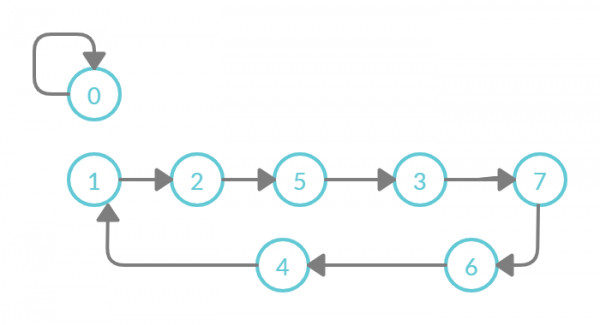

$4Q_2 + 2Q_1+Q_0$ is simply the decimal equivalent of state. Now, transition diagram can be drawn from above table as:

Correct State Sequence: 1,2,5,3,7,6,4.

Option (B) is correct answer.