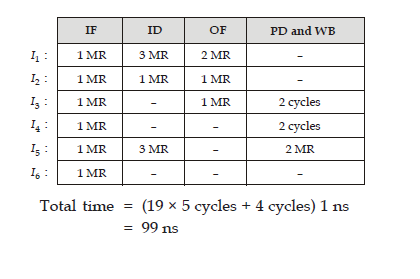

A pipeline model with stages IF (Instruction Fetch), ID (Instruction Decode), OF (Operand Fetch), PD (Perform operation in ALU and store result in a register) and WB (Write Back).

-

MOV r0, 4000 (I1): This is a memory reference operation, so it takes 5 cycles. It’s broken down into IF (1 cycle), ID (1 cycle), OF (1 cycle), PD (1 cycle) and WB (1 cycle).

-

ADD r0, r1, r2 (I2): This is an ALU operation, so it takes 2 cycles. It’s broken down into IF (1 cycle) and ID (1 cycle). The OF, PD and WB stages are overlapped with the next instruction due to pipelining.

-

STO r0, 5000 (I3): This is a memory reference operation, so it takes 5 cycles. It’s broken down into IF (1 cycle), ID (1 cycle), OF (1 cycle), PD (1 cycle) and WB (1 cycle).

-

MOV r3, 6000 (I4): This is a memory reference operation, so it takes 5 cycles. It’s broken down into IF (1 cycle), ID (1 cycle), OF (1 cycle), PD (1 cycle) and WB (1 cycle).

-

SUB r4, r3, r2 (I5): This is an ALU operation, so it takes 2 cycles. It’s broken down into IF (1 cycle) and ID (1 cycle). The OF, PD and WB stages are overlapped with the next instruction due to pipelining.

-

STO r4, 7000 (I6): This is a memory reference operation, so it takes 5 cycles. It’s broken down into IF (1 cycle), ID (1 cycle), OF (1 cycle), PD (1 cycle) and WB (1 cycle).

The total time required to complete the program execution is calculated as follows:

Total time = Time(I1) + Time(I2) + Time(I3) + Time(I4) + Time(I5) + Time(I6)

Total time = 19 * 5 cycles for memory reference operations + 4 cycles for ALU operations

Total time = 95 cycles + 4 cycles = 99 cycles

Since each cycle corresponds to 1 ns on a 1 GHz processor, the total time required to complete the program execution is 99 ns.

This solution takes into account the pipelining of instructions which allows multiple instructions to be executed simultaneously at different stages of execution. This is why the ALU operations only take up 2 cycles in the pipeline despite technically requiring more cycles for completion.