| Clock |

Q0 |

Q1 |

Q2 |

State |

| |

0 |

0 |

0 |

0 |

| 1 |

1 |

0 |

0 |

1 |

| 2 |

0 |

1 |

0 |

2 |

| 3 |

1 |

1 |

0 |

3 |

| 4 |

0 |

0 |

1 |

4 |

| 5 |

1 |

0 |

1 |

5 |

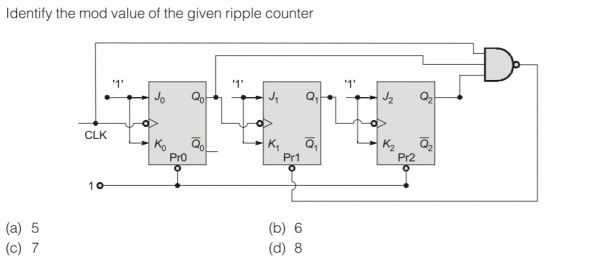

At clock t5 or lets say after 5 clock pulses Q0 and Q2 becomes 1 and through NAND gate they will become 0 and since preset is active low will set the contents to 000

Doubt - When will this happen? In clock t5 only? or in the next clock t6. What is the significance of connecting clock with NAND gate?

If the output is cleared in t5 only then MOD will be 5 if it happens in t6 then MOD will be 6.

Ideally we clear the flip flops in the same clock and hence 101 will not be a state. So the counter should be MOD-5 I guess. But does connecting clock to the gate play any significance role?

Doubt is similar to the one of the gate questions asked prviously : https://gateoverflow.in/1234/gate2007-36